APRIL 2020 VOL. 27, NO. 2 ISSN: 1074 1879

EDITOR-IN-CHIEF: DANIEL TOMASZEWSKI

| TABLE OF CONTENTS                                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Marvels of Microelectronic Technology:     From the Floating Gate and Charge Trapping concepts to the Flash Memory of Terabit class                               |

| UPCOMINGTECHNICAL MEETINGS                                                                                                                                        |

| SOCIETY NEWS                                                                                                                                                      |

| Awards and Call for Nominations                                                                                                                                   |

| VOUNG PROFESSIONALS                                                                                                                                               |

| CHAPTER NEWS COVID-19, How a Virus Affects the Science Community Region 8 IEEE EDS Distinguished Lecture Reports Region 10 IEEE EDS Distinguished Lecture Reports |

| REGIONAL NEWS                                                                                                                                                     |

| EDS VISION, MISSION AND FIELD OF INTEREST STATEMENTS                                                                                                              |

#### ECHNICAL

#### MARVELS OF MICROELECTRONIC TECHNOLOGY: FROM THE FLOATING GATE AND CHARGE TRAPPING CONCEPTS TO THE FLASH MEMORY OF TERABIT CLASS

BY SIMON DELEONIBUS, PAST CHIEF SCIENTIST CEA, LETI

#### Introduction

In this Technical Brief, we are focusing on the discovery, inventions and development of modern Non Volatile Memories (NVMs). Whereas, we reported on the invention and development of Dynamic Random-Access Memory (DRAM) in the October 2019 Newsletter issue.

Since the years 1990s to 2000s, NVMs, in their Flash Floating Gate and Charge Trap (FFG&CT) versions, have become the market and technology driver for integrated circuits as they entered the mass market through the camera, automotive and, further on, communication markets. Who among us has not used a USB key, a Solid State Disk (SSD), stored data on a mobile phone, or used a digital camera? No one can ignore today the formidable expansion of FFG&CT NVMs and the way they overcame the leadership on DRAM and Logic circuits as technology driver for Nanoelectronics. NVMs have gone through the highest number of conceptual and architectural changes in the past 50 years, evolving at the same time, from a niche product to a mass production driver. Just to give an example, Multi-Deca Gigabit (several tens of Gbit) USB keys, based on FFG&CT organized in a NAND architecture, are given almost for free nowadays as a storage and code share vector. Whereas, 256k NOR Erasable Programmable Read-Only Memory (EPROM), which were necessarily erased by using a UV lamp, were used for professional applications, essentially for storing microcontroller programs in the 1980s! Many hurdles have appeared in their 2-dimensional (2D) scaling, and today 3-dimensional (3D) multilevel cells (up to 4bits/cell) integration can increase the bit density without requesting conventional device scaling. The NAND FFG&CT memories have reached the Terabit integration level, using either an intermediate floating gate or pseudo floating gate charge trapping. Their market exceeded \$52B in 2018, which is unprecedented. They are on the way

#### **ELECTRON DEVICES** SOCIETY

#### President

Meyya Meyyappan NASA Ames Research Center E-mail: m.meyyappan@nasa.gov

#### **President-Elect**

Ravi Todi Western Digital Technologies Email: rtodi@ieee.org

#### Treasurer

Bin 7hao Freescale Semiconductor E-mail: bin.zhao@ieee.org

**Secretary** M.K. Radhakrishnan NanoRel E-mail: radhakrishnan@ieee.org

#### Jr. Past President

Fernando Guarin GlobalFoundries

E-mail: fernando.guarin@ieee.org

#### Sr. Past President

Samar Saha Prospicient Devices E-mail: samar@ieee.org

#### Vice President of Education

Navakanta Bhat Indian Institute of Science Email: navakant@gmail.com

#### Vice President of Meetings

Kazunari Ishimaru Kioxia Corporation

Email: kazu.ishimaru@kioxia.com

#### Vice President of Membership and Services

Patrick Fay University of Notre Dame E-mail: pfay@nd.edu

#### Vice President of Publications and Products

Joachim Burghartz Institute for Microelectronics Stuttgart E-mail: burghartz@ims-chips.de

#### Vice President of Regions/ Chapters

Murty Polavarapu Space Electronics Solutions E-mail: murtyp@ieee.org

#### Vice President of Strategic Directions

Paul Berger The Ohio State University E-mail: pberger@ieee.org

#### Vice President of Technical Committees

John Dallessase University of Illinois at Urbana-Champaign Email: jdallesa@illinois.edu

IEEE prohibits discrimination, harassment, and bullying. For more information, visit http://www.ieee.org/web/aboutus/whatis/policies/p9-26.html

#### **EDS Board of Governors (BoG) Elected Members-at-Large**

Elected for a three-year term (maximum two terms) with 'full' voting privileges

| 2020                                                                               | TERM                            | 2021                                                                                  | TERM                     | 2022                                                                 | TERM                     |

|------------------------------------------------------------------------------------|---------------------------------|---------------------------------------------------------------------------------------|--------------------------|----------------------------------------------------------------------|--------------------------|

| Roger Booth<br>Mukta Farooq<br>Edmundo<br>A. Gutierrez-D.                          | (1)<br>(2)<br>(1)               | Paul Berger<br>Navakanta Bhat<br>Merlyne De Souza                                     | (1)<br>(2)<br>(1)        | Constantin Bulucea<br>Daniel Camacho<br>John Dallesasse              | (1)<br>(1)<br>(1)        |

| Benjamin Iniquez<br>Carmen M. Lilley<br>Durga Misra<br>Manoj Saxena<br>Sumant Sood | (1)<br>(2)<br>(2)<br>(1)<br>(1) | Kazumari Ishimaru<br>William (Bill) Nehrer<br>Murty Polavarapu<br>Camilo Velez Cuervo | (1)<br>(1)<br>(2)<br>(1) | Mario Lanza<br>Geok Ing Ng<br>Claudio Paoloni<br>Hitoshi Wakabayashi | (1)<br>(1)<br>(1)<br>(1) |

#### NEWSLETTER **EDITORIAL STAFF**

#### **Editor-In-Chief**

Daniel Tomaszewski Institute of Electron Technology Email: dtomasz@ite.waw.pl

#### REGIONS 1-6, 7 & 9 Eastern, Northeastern & Southeastern USA

(Regions 1, 2 & 3) Rinus Lee GlobalFoundries

E-mail: rinuslee@ieee.org

#### Central USA & Canada (Regions 4 & 7)

Michael Adachi Simon Fraser University E-mail: mmadachi@sfu.ca

#### Southwestern & Western USA (Regions 5 & 6)

Editor Vacancy

#### Latin America (Region 9)

Edmundo A. Guiterrez-D. INAOE

E-mail: edmundo@inaoep.mx

#### **REGION 8**

Eastern Europe Kateryna Arkhypova IRE NASU

E-mail: arkhykate@ieee.org

#### Scandinavia & Central Europe

Marcin Janicki Lodz University of Technology

E-mail: janicki@dmcs.pl

#### United Kingdom, Middle East & Africa

Jonathan Terry The University of Edinburgh E-mail: jonterry@ieee.org

#### Western Europe

Mike Schwarz Robert Bosch GmbH E-mail: mike.schwarz1980@ googlemail.com

#### REGION 10 Australia, New Zealand & South East Asia

P Susthitha Menon Universiti Kebangsaan Malaysia E-mail: susi@ukm.edu.my

#### North East and East Asia

Ming Liu

Institute of Microelectronics E-mail: liuming@ime.ac.cn

#### South Asia

Manoj Saxena University of Delhi E-mail: msaxena@ieee.org

#### CONTRIBUTIONS WELCOME

Readers are encouraged to submit news items concerning the Society and its members. Please send your ideas/articles directly to either Editor-in Chief or the Regional Editor for your region. The e-mail addresses of all Regional Editors are listed on this page. E-mail is the preferred form of submission

#### Newsletter Deadlines

| <u>Issue</u>               | DUE DATE                             |

|----------------------------|--------------------------------------|

| July<br>October<br>January | April 1st<br>July 1st<br>October 1st |

| April                      | January 1s                           |

The EDS Newsletter archive can be found on the Society web site at http://eds.ieee.org/eds-newsletters.html. The archive contains issues from July 1994 to the present.

IEEE Electron Devices Society Newsletter (ISSN 1074 1879) is published quarterly by the Electron Devices Society of the Institute of Electrical and Electronics Engineers, Inc. Headquarters: 3 Park Avenue, 17th Floor, New York, NY 10016-5997. Printed in the U.S.A. One dollar (\$1.00) per member per year is included in the Society fee for each member of the Electron Devices Society. Periodicals postage paid at New York, NY and at additional mailing offices. Postmaster: Send address changes to IEEE Electron Devices Society Newsletter, IEEE, 445 Hoes Lane, Piscataway, NJ 08854.

Copyright © 2020 by IEEE: Information contained in this Newsletter may be copied without permission provided that copies are not used or distributed for direct commercial advantage, and the title of the publication and its date appear on each photocopy.

#### MARVELS OF MICROELECTRONIC TECHNOLOGY: FROM THE FLOATING GATE AND CHARGE TRAPPING CONCEPTS TO THE FLASH MEMORY OF TERABIT CLASS

(continued from page 1)

to replacing hard disk drives (HDDs) in computers and equipping data centers with Solid State Disks (SSDs).

Two major key persons that marked the history of Non Volatile Memories research and development, Professor Simon M. Sze, NCTU, IEEE Fellow, IEEE EDS Celebrated member (Figure 1a) and Professor Fujio Masuoka, Tohoku University, IEEE Fellow (Figure 1b), have kindly accepted to testify on the birth of the discovery of the floating gate effect and the invention of Flash Memories, respectively. Their testimonies are reported in sections 1 and 2. In section 4, members of the former team at Toshiba Memory (spun into Kioxia) who invented and first announced the 3D BICS-FLASH™ architecture graciously accepted to share their recollection.

#### 1. Simon Sze and the early cradle age of Floating Gate memories

Everybody in the semiconductor business knows Professor Simon Sze for his very popular and authoritative books, discoveries and inventions. The author of this Technical Brief accompanied his learning of semiconductor devices as an undergraduate student through Simon Sze's book titled Physics of Semiconductor Devices [1], first published in 1969, and is still using it daily as a reference just as many other scientists and engineers worldwide. Among the many seminal discoveries, inventions, studies and papers that Simon Sze authored in his career, the codiscovery of the Floating Gate Memory effect has certainly brought a revolution in our business and changed the societal way of living worldwide. Dawon Kahng and Simon Sze, Bell Labs researchers at that time, published a seminal paper in the Bell System Technical Journal in June 1967, in which they explained the Floating Gate

Figure 1 Recent portraits of: (a) Simon M. Sze (by courtesy of Simon Sze) (b) Fujio Masuoka (by courtesy of Fujio Masuoka)

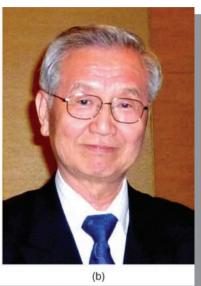

Memory (FGM) effect [2]. The device featured a 50 Å SiO, gate oxide, 1000 Å Zr floating gate, 1000 Å ZrO<sub>2</sub> coupling insulator and an Aluminum control gate. Pulses at 50 V and 0.5 µs were necessary to inject charge through the gate oxide from the Insulated Gate Field Effect Transistor (IGFET) channel into the floating gate, by capacitive coupling between the control gate and the floating gate (Figure 2a). Depending on the insulator, the charge injection (Figure 2b) was believed to be due to a Fowler-Nordheim (for example in SiO<sub>2</sub> or Al<sub>2</sub>O<sub>2</sub>) or Poole-Frenkel (Si<sub>2</sub>N<sub>4</sub>) mechanisms.

This was the very beginning of 60 years in research and development on the basic principle of charge storage/trapping in a stacked gate (1 control gate and 1 floating gate) device, and neutralization of the charge by an erasure mechanism, for example by applying an opposite voltage on the control gate. Without naming it explicitly, Kahng and Sze believed that such a device was announcing the Electrically Erasable Programmable Read-Only Memory (EEPROM). Many options and many divergent interests existed around the table without a dominant application really emerging at the beginning.

Since then, the Floating gate memory cell has proven to be the smallest memory device based on one transistor. It has beaten all predictions after being unrecognized or criticized as being expensive to make, unreliable and incompatible with logic devices, due to high program/erase voltages, and thus necessarily using a thick gate oxide susceptible to being stressed and suffering from induced defects. Nowadays, on the contrary, it has become a commodity product offering programmable/erasable mass storage media after 50 years of continuous struggle and studies.

In the frame of our exchanges, Prof. Simon Sze explained the motivations that led him and D. Kahng to invent the floating gate device for memory applications: "In the

Figure 2(a) First floating-gate memory (FGM) by Dawon Khang (left) and Simon Sze (right).

(Courtesy of Simon Sze) and Figure 2(b) Band diagram of a Floating gate transistor structure during: (a) charge trapping, (b) storage and (c) detrapping

(discharging) (Courtesy of Simon Sze)

Figure 3(a) MNOS structure (Wegener et al.): discrete charge trapping devices (Courtesy of Simon Sze) and Figure 3(b) Floating gate Avalanche-injection MOS (FAMOS) structure [6]

mid 1960's, magnetic core memory (MCM) was used in computers. It took a long time to turn on the mainframe computer (m/c). We thought a semiconductor memory should be faster than the MCMs to boot up the mainframe computer (m/c)." Simon Sze adds: "When we submitted our paper to BSTJ in May 1967, we really did not know that FGM would eventually supersede all prior non-volatile memory technologies (e.g. magnetic tapes, HDDs, optical disks) and in early 21st century ush-

ered in the 4th Industrial Revolution and brought unprecedented benefit to the mankind." The paper introduced not only the basic concept of non-volatility in semiconductor devices, but also the floating-gate structure which is still the dominant technology for nonvolatile information storage.

In those days, many engineers and researchers wanted to use Read Only Memories for code storage by an electrical action, without necessarily being able to erase and program

again. That is why the devices were pointed out as "alterable memories". Coincidentally with Kahng and Sze's discovery, in December 1967, H.A.R. Wegener from Sperry Rand Research Center published research on the Metal, Nitride Oxide Silicon (MNOS) transistor [3] in which charges were stored in silicon nitride layer traps by the Poole-Frenkel transport, after injection through the underlying tunnel oxide (Figure 3a). It resulted in a memory device with low charge retention capabilities, due to leakage through the gate. Other authors reported similar structures [4]. Keshavan and Lin reported on the band gap engineering of the insulating stack by introducing an extra oxide layer between the gate and channel, resulting in a MONOS structure [5]. The extra layer avoided charge leakage from the nitride to the gate and modified the transistor threshold voltage as well.

From the 1960's to the beginning of the 1970s, only mask writable memories (Read Only Memories or ROMs) were available. Electrically programmable/erasable devices were still confined in their infancy. In 1971, Intel proposed a 2kBit Floating gate Avalanche-injection MOS (FAMOS) memory [6], without a control gate, to store charge from the MOSFET drain (Figure 3b) by using a carrier injection from the avalanche current at the drain. Pulses of 50 V for 5 ms, with a load current of 50 mA, were necessary to program 1 bit. The memory was UV erasable collectively but still needed to be programmed bit by bit, due to its NOR gate architecture. However, the absence of a control gate could not make it electrically erasable.

#### 2. The advent of Flash memories

Fujio Masuoka was an intellectually precocious child, especially good at math, had overwhelming capacities by three years in advance at the school and high school levels. He was thus a very curious spirit and certainly keen to taking risky paths for innovation. Early

in his career at Toshiba, he worked on DRAM as a development engineer as well as a salesman.

At that time, Ultraviolet (UV)-EPROM and EEPROM were available. However, there were cost per bit issues with UV-EPROM and EEPROM. EEPROM needed a much more complex architecture (two transistors) than UV-EPROM, which were more compact and scalable. However, UV-EPROMs posed more constraint at the system level (UV collective erasing) and made them less popular.

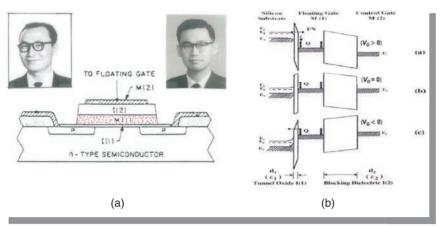

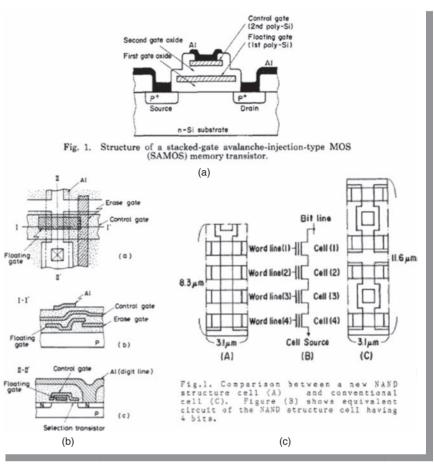

"My idea on EPROM was that programming can be performed at a lower voltage and a higher speed than that of the conventional EPROM, by using a control gate. In the invention USP 3,825,945 I claimed that the capacitance between the floating gate and control gate should be larger than that between the substrate and floating gate [7]" says Masuoka. An increased coupling ratio (ratio between the control gate/floating gate capacitance and floating gate/ substrate capacitance) resulted in enhanced charge injection into the floating gate from the device channel. Moreover, Masuoka and lizuka proposed to use stacked polysilicon electrodes separated by a coupling insulator to implement the control and a floating storage gate [8-10], in a one transistor cell programmable in a drain avalanche mode. The Stackedgate Avalanche-injection MOS (SA-MOS) memory established a direct link with polysilicon gate CMOS, which was becoming the mainstream technology (Figure 4a). These conditions, put together, formed the concept for a future commodity-like product that was never thought, but finally proven to be capable of competing with DRAM in terms of density and cost per bit, even though not as fast. The success of the digital cameras, of the flexibly mobile mass storage in the form of USB keys, and of mobile phones, boosted the demand for such devices easily usable by the public at large. This demand was enabled by Flash Memories. However,

Figure 4 (a) SAMOS structure [9] programmable by charge injection resulting from drain avalanche breakdown and electrically or UV erasable—partially presented at IEDM 1972 late news; (b) First paper on Triple poly Flash Memory (NOR gate), presented at IEDM 1984 [12]; (c) First paper on NAND type Flash Memory, presented at IEDM 1987 [15]. Comparison between NOR and NAND gates layout. will be details of Fig.4b visible after printing?

at this point, still the "battle was not won"!

In the early 1980s, the EEPROM required two transistors per bit (a non-volatile memory transistor and a select transistor) necessarily bit by bit rewritable. How could each bit be reduced to one non-volatile memory transistor only to reduce the bit cost? "The cost per bit could drop much lower to a quarter," declares Masuoka who paradoxically underlines: "I noticed that by erasing all bits at once, and then writing bits on a per-bit basis, a select transistor would not be needed. This marked the advent of electrically-rewritable Flash Memory, which can be erased all at once, with only one non-volatile memory transistor for each bit, granted as USP 4,437,174 [11]." This conclusion was counterintuitive even for many professionals because erasing all bits in a sector to change one was seen as a "waste of time". The erasure was obtained by injecting electrons by field emission between the control gate and a third polysilicon erase gate. Actually, at the small scale of writing/erasing times, collective Flash erasure was not an issue and was energy wise efficient. The working principles behind NOR flash memory were presented at the 1984 IEDM [12] (Figure 4b), and 256-kbit NOR flash memory was announced at the 1985 ISSCC [13].

Masuoka adds: "In 1986, I eventually noticed that NOR flash memory was so insufficiently low cost that it could not drive out magnetic disks, and that the Flash Memory should be needed to further reduce the cell area per-bit. The answer was NAND Flash Memory, granted as USP 5,245,566 [14]. In April 1987, I successfully verified the basic properties of the NAND flash memory, namely writing, reading and erasure by bulk injection." The results were presented at the 1987 IEDM [15] (Figure 4c)

Masuoka wanted to quickly prototype a 4Mbit NAND Flash circuit, but had a hard time to convince his management to provide mask funding. He failed to get any funding from the computer division, because they found the concept too ambitious to replace magnetic storage memories.

"If I'd given up there, all my work up to then would have come to nothing," confesses Masuoka. He found an ally at the Consumer Electronics Division to financially support his project: "I explained to Mr. Tajiri, Director of the Consumer Electronics Laboratory, that if we managed to produce 4-Mbit NAND flash memory, cameras would no longer need film. I was indeed explaining that the digital cameras which we know today would become possible. We successfully developed 4-Mbit NAND flash memory in 1988 and announced 4-Mbit NAND flash memory at the ISSCC in February 1989 [16]. Thereafter, Mr. Tajiri used the 4-Mbit NAND Flash memory to launch the world's first digital camera to replace conventional film with NAND flash memory. At the time, the price of the flash memory was high and the world's first flash memorybased camera didn't sell well."

Masuoka finally concludes: "Now, Flash Memory is penetrating into the whole economic framework. The world-wide market size of the NAND Flash Memory last year surpassed \$52B. In the near future it is expected to become more than \$100B, which is unmatched in the history of the world, when all the HDD's in the personal computers are replaced by the SSDs, and the HDD's of the data station of Google and FaceBook, etc. are partially replaced by the SSDs. This is because the market share of not only the semiconductor memo-

ry but also the HDDs is accounted. And also, many power stations in the world can be saved by replacing the HDD by the SSD. For this is what the final target of the NAND Flash Memory is all about, and there is no doubt at all that the NAND Flash Memory is an earth-conscious 'Green Technology'."

#### 3. Looking for new breakthroughs in process integration

At the beginning of the years 2000, the guest for an efficient solution to increase the capacity of floating gate based Flash Memories beyond the 70-50 nm node has been an ongoing question. As a matter of fact, the high voltage used for cell programming/erasing and the floating gate architecture itself, imposed insulators thicker than for logic devices to withstand the reliability constraints. Such a situation made the floating gate transistors more sensitive to short channel effects and to a retention and endurance degradation due to Stress Induced Leakage Current (SILC). Cell to cell disturbance increased with spacing reduction. At such a point, several alternatives were making sense to move aside the necessity of 2D linear scaling to increase memory capacity. Beyond stacking 2D memory arrays in a package, other device architecture or integration based solutions were being developed. One idea was to increase the number of bits per cell [17] by programming several states corresponding to several threshold voltages to read, the limit being the threshold voltage distribution variability and the associated noise margins. Nowadays, up to 4 bits per cell are implemented in large capacity SSD circuits (see hereunder). Another way was to stack 2D arrays at the chip level [18], with a limit in a cost per bit reduction approach.

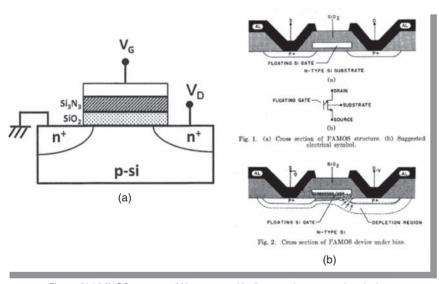

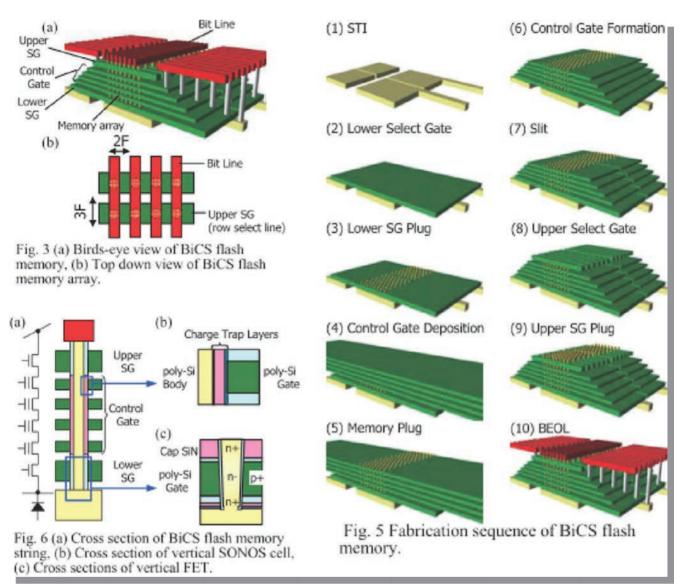

Finally, a multiplication of vertical 3D strings Flash architecture was proposed by Toshiba [19] by the so called Bit Cost Scalable (BiCS) technology, renamed BiCS FLASH™. The

vertical gate-all-around transistor architecture with discrete traps (pseudo floating gates) storage had a higher electrostatic integrity than the conventional 2D architecture. Moreover, the vertical gate-all-around structure did not require such aggressive lithography capabilities to increase the final circuit capacity and resulted in a highly competitive cost per bit.

### 4. Three Dimensional (3D) Flash Memory: BiCS FLASH™ at TOSHIBA's memory division¹

At Toshiba, the BiCS FLASH™ technology was developed as soon as July 2005 when the first idea came out. Toshiba announced the first example of a vertical channel based high density Flash memory array, featuring gate all-around transistors and a SONOS like gate stack structure. As in all major memory companies, there were discussions on different options to solve the scaling issues of 2D Flash Memories: an increasing transistor variability, a program disturbance due to neighboring cell interferences, and an increasing fabrication tools cost. Options such as 3D stacked floating gates, FeRAM, ReRAM, PCRAM were being considered in the discussion. In that context, a cross-point architecture was published by Matrix Semiconductor (now Sandisk), composed of crossbar type one-time programmable memory cells, stacked repeatedly [20]. At that time, Hideaki Aochi was leading a non volatile memory process integration team at Toshiba. Note that the company has recently spun off its memory business by creating KIOXIA.

Aochi, now a KIOXIA engineer, recalls: "The cross point architecture needed a large number of process steps, because of the large number of repetitions of the similar crossbar shaped memory structure. A large fabrication chip cost was a severe issue."

¹ Currently spun off from Toshiba and renamed as

Figure 5 First publication of the BiCS FLASH™ Memory technology at VLSI Technology Symposium in June 2007 [19].

Aochi remembers: "One day, during my ride in the commuter train, I had gotten the basic idea of punch and plug process to make a hole thru many stacked layers of two different materials. Then our team had started to construct all the elements of the basic concept of BiCS FLASH™, which are: detailed process integration, device design, array structure, staircase layout, and row/column wiring connection to driver and sensing circuit." (Figures 5, 6).

Many questions arose while starting to implement such a seductive idea: the impact of a polysilicon channel on variability and the process integration of a vertical gate-all-around transistor. Since the 1980s, at the time of advent of thin film p-channel transistors load for Static RAMs or displays row- and column-select transistors. the use of polysilicon channels in the fabrication of logic or memory circuits of ULSI densities was highly challenging and many questions existed around on a possible variability issue. These types of devices were better known in the field of displays but for much larger geometries.

Aochi says: "After some experiments, we realized that the variability of transistor performance had been caused by two major factors, one was due to the poly-Si channel, as we had expected, and the other was the contact resistance of the connection of the poly-Si channel to the substrate."

The solution was to give a hollow tubular shape to the memory strings and to thin down the polysilicon channel to keep electrostatic integrity, just as in a thin body SOI transistor. Typical macaroni shaped channels were thus implemented. A pipe-shaped string structure could eliminate the bottom contact of the poly-channel

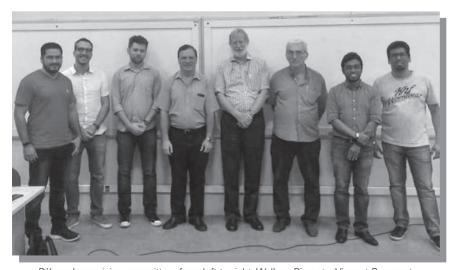

Figure 6 Members of the BiCS FLASH<sup>TM</sup> Memory team celebrated at KIOXIA. From left to right: (Lower row) Masaru Kito\*, Tomoharu Matsushita\*\*,

Hideaki Aochi\*, Hiroyasu Tanaka\*, Akihiro Nitayama\*, Ryota Katsumata\* and (Upper row) Masaru Kido\*;

\*Inventor, \*\* Chief Production Executive of KIOXIA Corporation (by permission of KIOXIA)

to the substrate and stabilize the variability of the contact resistance.

The first results of an experimental 512 kbit test chip were presented at the 2007 VLSI Symposium [19]. The team was successful in presenting the results of functional 32 Gbit density memory arrays, obtained in 2008, at the 2009 VLSI Technology Symposium [21].

Aochi underlines: "That announcement impacted all of flash memory manufacturing and accelerated similar type of flash memory development. We had made the first production chip of 48-layers of BiCS FLASH™ with 256 Gbit memory density in 2015." Obtaining reproducible hole shape strings was a major critical path.

Toshiba announced at ISSCC 2019 a 1.33 Tbit chip based on the 3D BiCS FLASH™ technology stacking 96 layers and 4 bit/cell [22].

After the successful implementation of the BiCS-FLASH™ technology by Toshiba and continued by Kioxia, 3D vertical Flash memories have become very popular for mass storage among the main memory makers. After producing stacked 2D structures [18], Samsung followed an approach close to Toshiba's and demonstrated a vertical 3D structure integrating a damascene p+-like W gate, ancestor of a vertical TaNOS structure [23].

Nowadays, 3D Terabit class memory can be integrated in a single chip,

stacking up to 128 layers, featuring up to 4 bits/cell and a bit surface density approaching 10 Gbit/mm². The memory circuits can be handheld in a solid state disk or equip mass storage systems in data centers. The 3D string-type Flash Memories have been adopted among Toshiba/KIOXIA competitors as well, either with a SO-NOS/p+-like TaNOS or vertical Floating gate structures [23]–[26].

Many other candidates featuring alternative structures or materials have been trying to take over their success. These are floating gate-inspired (i.e. Si Nanocrystal FG, split gate, NROM structures, etc.) or based on 1 to 2 transistors associated to a resistor or capacitor(s) (i.e. MRAMs, STT RAMs, ReRAMs, FeRAMs, etc.) to reduce the SILC issue or address a storage node. Their compatibility or co-integration with Si CMOS is sometimes a strong requirement. Some of these alternative solutions could be or have already been adopted as application specific, field programmable gate arrays (FPGAs), embedded memories or distributed in CMOS for new computing paradigms and ultra low power circuit architectures (i.e. neuromorphic computing and programmable circuits, non-volatile logic and RAMs, etc.) [27]. These latter topics have not been addressed in this issue, due to the vast extent of the subject, as they would request another article.

The discovery of the Floating Gate and discrete trapping concepts augmented by the invention of Flash Memories are with no doubt major events in the history of microelectronics and its success. They have sustainably impacted our daily life with broad societal usage. Their most recent success for 3D mass storage was possible thanks to a succession of microelectronics engineering marvels developments.

Acknowledgements to Prof. Simon Sze (NCTU), Prof. Fujio Masuoka (Tohoku University), Dr. Koji Sakui (Honda), Prof. Masaaki Inutake (Tohoku University), Drs. HiroyasuTanaka, Ryota Katsumata, Hideaki Aochi, and Kazunari Ishimaru (KIOXIA).

#### References

[1] S.M.Sze, "Physics of Semiconductor Devices", Ed. John Wiley and Sons Inc., New York (1969).

[2] D. Khang and S.M. Sze, "A floating gate and its application to memory devices," *Bell Syst. Tech. J. Briefs*, pp.1288–1295, vol. 46, Aug. 1967.

[3] H. A. R. Wegener, A. J. Lincoln, H. C. Pao, M. R. O'Connell, R. E. Oleksiak, H.Lawrence, "THE VARIABLE THRESHOLD TRANSISTOR, A NEW ELECTRICALLY-ALTERABLE, NON-DESTRUCTIVE READ-ONLY STORAGE DEVICE," Digest. Tech. papers IEDM 1967, #11.4, p.70.

[4]. J.R. Szedon and T.L. Chu "Tunnel Inspection and Trapping of Electrons in

Aluminum-Silicon Nitride-Silicon Dioxide-Silicon (MNOS) Capacitors," Abs. Solid State Device Research Conference, p 631, 1967.

[5] B.V. Keshavan and H. C. Lin, "MONOS MEMORY ELEMENT," IEDM Digest of Technical Papers, pp. 140-141, Oct 1968.

[6] D. Frohman-Bentchkowsky "A fullydecoded 2048-bit electrically-programmable MOS ROM," IEEE ISSCC Digest of Technical Papers, pp. 80-81, Feb. 1971 and IEEE JSSC pp 301-306, Oct 1971.

[7] F. Masuoka, "Field Effect Semiconductor Memory Apparatus with a Floating Gate," USP 3,825,945, July 23, 1974.

[8] H. Iizuka, T. Sato, F. Masuoka, K. Ohuchi, H. Hara and Y. Takeishi, "A Fully-Decoded 2048-Bit Avalanche-Injection Type, Electrically Alterable ROM," IEDM Tech Digest pp. 4-5, 1972.

[9] H. lizuka, T. Sato, F. Masuoka, K. Ohuchi, H. Hara and Y. Takeishi, "A Fully-Decoded 2048-Bit Avalanche-Injection Type, Electrically Alterable ROM," IEEE TRANSACTIONS ON ELECTRON DE-VICES, VOL. ED-23, NO. 4, pp.379-387

[10] F. Masuoka and H. Iizuka, "Semiconductor Memory Device," USP 4,115,795, Sep. 19, 1978.

[11] F. Masuoka, "Semiconductor Memory Device," USP 4,437,174, Mar. 13, 1984.

[12] F. Masuoka, M. Asano, H. Iwahashi, T. Komuro and S. Tanaka,"A new Flash EE-PROM cell using triple polysilicon technology," IEEE Tech. Dig. IEDM 1984, pp. 464-467

[13] F. Masuoka, M. Asano, H. Iwahashi, T. Komuro and S. Tanaka, "A 256K Flash EEPROM using triple polysilicon technology," IEEE ISSCC 1985, pp. 168-169.

[14] F. Masuoka, "Programmable Semiconductor," USP 5,245,566, Sep. 14, 1993. This patent showed NAND Flash Memory.

[15] F. Masuoka, M. Momodomi, Y. Iwata, and R. Shirota, "New ultra high density EPROM and Flash EEPROM cell with NAND structure cell," in IEEE Tech. Dig. IEDM 1987, pp. 552-555.

[16] Y. Itoh, M. Momodomi, R. Shirota, Y. Iwata, R. Nakayama, R. Kirisawa, T. Tanaka, K. Toita, S. Inoue, and F. Masuoka, "An experimental 4Mb CMOS EEPROM with a NAND structured cell," IEEE Int. Solid-State Circuits Conf., 1989, pp. 134-135.

[17] M. Bauer, R. Alexis, G.Atwood, et al., "A Multilevel-Cell32Mb Flash Memory," Tech Digest IEEE Int. Solid-State Circuits Conf, 1995, p132-133.

[18]. SM Jung, J Jang, W Cho et al., "Three dimensionally stacked NAND flash memory technology using stacking single crystal Si layers on ILD and TANOS structure for beyond 30nm node," Tech Digest IEDM, 2006, p37-40.

[19]. H.Tanaka, M.Kido, K.Yahashi et al., "Bit Cost Scalable Technology with Punch and Plug Process for Ultra High Density Flash Memory," Symp. on VLSI Tech. Dia., pp14-15, 2007.

[20] Mark Johnson, Ali Al-Shamma, Derek Bosch et al., "512-Mb PROM With a Three-Dimensional Array of Diode/Antifuse Memory Cells," IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 38, NO. 11, pp.1920-1928, NOVEMBER 2003.

[21] Ryota Katsumata, Masaru Kito, Yoshiaki Fukuzumi et al., "Pipe-shaped BiCS Flash Memory with 16 Stacked Layers and Multi-Level-Cell Operation for Ultra High Density Storage Devices," Symp. on VLSITech. Dig, pp 136-137, 2009.

[22] N. Shibata, K. Kanda, T. Shimizu et al., "A 1.33Tb 4-bit/Cell 3D-Flash Memory on a 96-Word-Line- Layer Technology," ISS-CC 2019Tech Digest,pp 210-212.

[23]. Jaehoon Jang, Han-Soo Kim, Wonseok Cho, et al., "Vertical Cell Array using TCAT (Terabit Cell Array Transistor) Technology for Ultra High Density NAND Flash Memory," Symp on VLSI Technology Symp. Digest of Technical papers, (2009), pp 192-193.

[24] D-H. Kim, H. Kim, S. Yun, Y. Song et al., "A 1Tb 4b/Cell NAND Flash Memory with  $t_{PROG} = 2ms$ ,  $t_{R} = 110 \mu s$  and 1.2Gb/s High-Speed IO Rate," To be published at IEEE ISS-

[25] H. Huh, W. Cho, J. Lee, Y. Noh et al. "A 1Tb 4b/Cell 96-Stacked-WL 3D NAND Flash Memory with 30MB/s Program Throughput Using Peripheral Circuit Under Memory Cell Array Technique," To be published at IEEE ISSCC 2020.

[26] K. Parat and A. Goda, "Scaling Trends in NAND Flash," IEDM Tech. Dig., pp. 2.1.1-2.1.4, 2018.

[27] S. Deleonibus, O. Faynot, T. Ernst et al., "Future Challenges and Opportunities for Heterogeneous Process Technology. Towards the Thin Films, Zero Intrinsic Variability Devices, Zero Power Era," IEDM Tech. Dig., pp. 9.2.1-9.2.4, 2014.

IMPORTANT: THE CONFERENCE NOTICES IN OUR SOCIETY NEWSLETTER WERE PUBLISHED BEFORE THE ESCALATION OF THE COVID-19 PANDEMIC. MANY IEEE CONFERENCES ARE ALTERING THEIR ARRANGEMENTS. PLEASE CONSULT EACH CONFERENCE WEBSITE FOR THE MOST UP-TO-DATE INFORMATION.

#### UPCOMING TECHNICAL MEETINGS

### 2020 IEEE PHOTOVOLTAICS SPECIALIST CONFERENCE (PVSC)

BY SETH HUBBARD AND GEOFFREY BRADSHAW

It is our great pleasure to invite you to attend the 47th IEEE Photovoltaics Specialists Conference, which will be held from June 14–19, 2020, at the Telus Convention Center in Calgary, Alberta, Canada.

We live at a special time when solar electricity has become cost competitive with conventional electricity in many locations, enabling remarkable growth of the industry. As was the case in 2017, solar was the biggest contributor to net expansion of electricity generating capacity in 2018. In fact, the IEA PVPS has recently reported that worldwide solar installed capacity has now crossed the halfTW mark! The 47th IEEE PVSC will help sustain this fantastic momentum with over 800 technical papers from around the world, reflecting today's dynamic and expanding markets. The PVSCs have a rich tradition of bringing together students, innovators, researchers and PV leaders in a vibrant and highly integrative forum to share information, gain knowledge, strengthen collaborations and move forward photovoltaic science and technology from basic and applied research into large scale manufacturing and deployments.

If you would still like to contribute technically, please submit your abstract before our late news deadline on April 20, 2020.

Continuing with the tradition of the past few years, the 47th IEEE PVSC will

Calgary, Canada skyline

be divided into 12 technical areas covering cutting-edge developments in science and engineering of photovoltaics, ranging from fundamentals to applications, with an emphasis on material science, devices, systems, solar resources and policy related matters. PVSC-47 aims to be a highly interactive venue for both seasoned PV experts as well as entry-level professionals and students. The conference provides a unique opportunity to meet, share and discuss PV-related developments in a timely and influential forum. Please consider contributing to the PVSC's tradition as the premier international conference on PV science and technology and help us propel the world towards power from the Sun. As well, we will be presenting the prestigious William R. Cherry Award, honoring the photovoltaics communities' most outstanding scientist or engineer as well as the Stuart R. Wenham Young Professional Award for individuals who have made significant contribution at an early stage of their career.

The conference Exhibition will showcase the latest developments in PV characterization and manufacturing equipment, and is set to further enhance attendee awareness on latest tools and instrumentation as well as to facilitate exchange between scientists, technical experts and exhibitors.

We are very excited to host the first ever PVSC to be held in Canada. Calgary is a beautiful city in the heart of Canada situated on the eastern slope of the magnificent Canadian Rockies mountain range. As the fourth-largest and the sunniest city in Canada, Calgary has a lot to offer visitors from around the world. Calgary has one of the highest concentrations of green space in North America, and is the first municipality in Canada to power its infrastructure solely by renewable energy.

(continued on page 13)

#### REGISTER Now FOR THE IEEE IITC 2020 CONFERENCE

IITC 2020 will be held June 1-4, 2020 in the heart of Silicon Valley at the newly renovated campus of the Holiday Inn San Jose-Silicon Valley, easily accessible from San Jose International Airport. One of the highlights will be a special evening event at The Tech Interactive in downtown San Jose.

IITC is the premier conference for interconnect technology and will offer leading-edge research in the field of advanced metallization and 3D integration for ULSI IC applications. The conference will highlight innovative research and development in the critically important field of on-chip interconnects, integration and metallization, including design, unit process, integration and reliability.

The conference will kick off with a one-day workshop on June 1st:

#### Model Your Way to a Better **Backend Technology Workshop Program**

In this workshop, leading scientists and innovators will review the modeling approaches used in industry and academia, providing a powerful

means to predict the performance of continuous scaling and integration of new interconnects and memories on chip. They will also show benchmarking of various materials and device technologies.

#### We are excited to have the following Keynote Speakers:

- Dr. H.-S. Philip Wong, VP of Corporate Research at TSMC and the William R. and Inez Kerr Bett Professor at Stanford University.

- Dr Michael Mayberry, Chief Technology Officer and Senior VP and GM of Technology Development at Intel.

#### Our Invited Speakers include:

- Jeong-Hoon Ahn, Samsung

- Kristof Croes, imec

- Suman Datta, University of Notre Dame

- Regina Freed, Applied Materials

- Arnaud Furnemont, imec

- Oleg Gluschenkov, IBM

- Chris H. Kim, University of Minnesota

- Eiich Kondoh, University of Yamanashi

- Nick Lanzillo, IBM

- Takeshi Nogami, IBM

- Jon Reid, Lam Research

- Harsono Simka, Samsung

- Shintaro Yamamichi, IBM Japan Presentation topics for invited speakers may be found on at https:// iitc-conference.org/invited-speakers/

Full conference and workshop details may be found at https://iitc-conference.org

#### IITC 2020 is sponsored by the IEEE Electron Devices Society. Registration:

Conference registration is now open at https://iitc-conference.org/registration/ Early Registration deadline: May 8, 2020

#### **IITC-2020 Conference Co-Chairs:**

Paul Besser, Robert Socha and Soo-Hyun Kim

# THE 2020 SYMPOSIUM ON VLSI TECHNOLOGY LOOKS AHEAD TO "THE NEXT 40 YEARS OF VLSI FOR UBIQUITOUS INTELLIGENCE" IN HONOLULU, HAWAII

The premier international conference on VLSI semiconductor technology is celebrating its 40th year of delivering unique perspectives on the convergence of VLSI technology in the microelectronics industry. The 2020 Symposia on VLSI Technology & Circuits is organized on the theme: "The Next 40 Years of VLSI for Ubiguitous Intelligence," and will be held from June 14th to 19th, 2020, at the Hilton Hawaiian Village in Honolulu, Hawaii, USA. The symposia are jointly sponsored by the IEEE Electron Device Society (EDS) in cooperation with the IEEE Solid-State Circuits Society (SSCS) and the Japan Society of Applied Physics.

Held jointly on a fully-overlapping schedule from June 14th to 19th, 2020 in Hawaii with the Symposium on VLSI Circuits, the two Symposia integrate advanced technology developments, innovative circuit design, and the applications they enable, such as machine learning, IoT, artificial intelligence, wearable/implantable biomedical applications, big data, cloud/edge computing, virtual reality (VR)/augmented reality (AR), robotics, and autonomous vehicles. As such, the combined Symposia provide a unique perspective that promotes interactions between technologists and circuit/system designers, reflecting the close relationship between R&D in both areas required to achieve continuous improvement in performance, power efficiency, connectivity, and cost reduction. This integration between innovations in devices and circuits helps foster new technologies, processes, and applications. A single registration fee covers both events.

As part of this integration, this year the Symposia will once again feature special joint focus sessions to provide opportunities for both

Rainbow Tower, Hilton Hawaiian Village, Honolulu, Hawaii - a venue of the 2020 VLSI Symposia

Technology and Circuits attendees to exchange ideas on areas of joint interest that enable ubiquitous intelligence, smart mobility, and other VLSI applications, including: "MRAM Future: Beyond STT, Beyond Embedded," "Silicon Photonics," "5G/mmwave," "System/Design-Technology Co-Optimization," "Artificial Intelligence/Machine Learning," and "Heterogeneous Integration."

Once again, the Symposia will be followed by a full-day Friday Forum session dedicated to "Technologies & Circuits for Edge Intelligence," led by experts in the field who will help guide participants in discussions on the contributions of technology and circuits needed to drive the future of advanced edge computing.

Additional highlights include:

Plenary sessions for both Technology and Circuits with four talks:

Dr. Michael C. Mayberry, chief technology officer at Intel Corporation, "The Future of Compute: How the Data Transformation is Reshaping VLSI,"

- Takehiro Nakamura, senior vice president & general manager of 5G Laboratories, NTT DOCOMO, "5G Evolution and 6G,"

- Shigeo (Jeff) Ohshima, technology executive at KIOX-IA (formerly Toshiba Memory), "Empowering Next-Generation Applications through FLASH Innovation"

- Jen Lloyd, vice president for the Precision Technology & Platforms Group, Analog Devices, "Performance that Matters at the Real World Interface."

#### **Three Evening Panel Discussions:**

- "40 Years of VLSI to Enable the Future of Computing"

- "Memory & LogicTechnology Divergence: Will Al/ML BringThem BackTogether?

- "Human vs. Machine: The Future Role of Al/Machine Learning in Circuit Design"

Full-day short courses. Attendees will learn about recent trends and challenges in advanced microelectronics

technology and its adaptation into new computing systems:

- "Future of Scaling for Logic & Memory

- "System, Technology, & Design Solutions for Heterogeneous Integration"

- "Trends & Advancements in Circuit Design"

Sunday Workshops. (Held June 14th before the technical sessions):

- "Know Where You Are Going: Metrology in the New Age of Semiconductor Manufacturing"

- "Analog Computing Technologies & Circuits for Efficient Machine Learning Hardware"

"Quantum Computing: Maximizing the Impact of the Semiconductor Industry"

Satellite workshops (held before the technical session of the symposium):

- "IEEE Silicon Nanoelectronics Workshop" (June 14th & 15th)

- "Spintronics Workshop on LSI" (June 14th) at the same location.

We cordially invite you to attend the 2020 Symposium on VLSI Technology. For further information please visit the VLSI Symposia website: www .vlsisymposium.org.

Technology Symposium Chairman: Chorng-Ping Chang (USA)

**Applied Materials** Technology Symposium Co-Chairman'

Yamakawa Shinya (Japan) Sony Semiconductor Solutions Technology Program Chairman: Tomas Palacios (USA) Massachusetts Institute of Tech-

nology

Technology Program Co-Chairman: Katsura Miyashita (Japan) Toshiba Electronic Devices & Storage

#### 2020 IEEE PHOTOVOLTAICS SPECIALIST CONFERENCE (PVSC)

(continued from page 10)

Don't miss out on the opportunities offered by the conference social gatherings and networking events to get to know your colleagues better, reconnect with old friends and make new ones. The week kicks off with our Exhibitor Reception on Monday evening at the Convention Center and will conclude with a Conference Reception on Thursday evening to be held at Calgary's Glenbow Museum, with exhibits and performances that bring the art and culture of Calgary to life.

On behalf of the Organizing, Cherry, and International Committees, we look forward to welcoming you to the 47th PVSC in Calgary, Canada!

Further details and registration can be found at https://www.ieee-pvsc .org/PVSC47/

Seth Hubbard Conference General Chair Rochester Institute of Technology

> Geoffrey Bradshaw Conference Publicity Chair Pike Engineering, LLC

Dear EDS Newsletter Readers.

Due to the global pandemic, many conferences are altering their arrangements. Due to this fact, we did not publish the Technical Meeting Calendar in this issue. We are very sorry for this. Please consult each conference website for the most up-to date information. We do hope that people and organizations involved in a campaign against the SARS-CoV-2 worldwide will succeed in the near future. We wish all the best to you and to your beloved.

**EDS Newsletter Editorial Team**

#### SOCIETY NEWS

#### A MESSAGE FROM EDITOR-IN-CHIEF

Dear EDS Members and Readers,

Daniel Tomaszewski Editor-in Chief, EDS Newsletter

The IEEE Electron Devices Society (EDS) is a world-wide community of experienced researchers and engineers, young professionals, and students working in the area of electron device

(ED) technology. Our community needs a platform for sharing news about global and local initiatives and undertakings in this field and for sharing information on the Society growth with emphasis on the EDS chapter activities, taking into account their professional and societal aspects. EDS Newsletter serves as such a platform for the benefit of the EDS healthy and sustainable growth.

I have been involved in the EDS Newsletter activity since 2015. Then Dr. Wladek Grabinski recommended me for a position of EDS Newsletter Regional Editor for Region 8 Eastern Europe. After a positive evaluation of my candidacy by the Newsletter Oversight Committee, Dr. M.K. Radhakrishnan, Editor-in-Chief invited me to join the Editorial Board. Since then, I have constantly experienced a very kind support and leadership from M.K.R. and next, from Dr. Carmen Lilley as Editors-in-Chief, as well as a kind assistance from Joyce Lombardini coordinating a work of the Editorial Board. I am deeply grateful to them for the collaboration and guidance. In October 2019 I was asked, surprisingly for me, whether I agreed to candidate for the Editor-in-Chief position. I agreed ... and was approved for a three-year term. Here I have to express my gratitude and thanks to colleagues from EDS Chapters in Georgia, Macedonia, Ukraine, Romania, Russia with whom I was collaborating since 2015. They do have a significant contribution to this nomination.

So, a new challenge for me with an incomparably larger scope of responsibilities has appeared. I am aware, that I will be able to fulfill my duties and meet the requirements only if I follow the rules and procedures, and closely collaborate with the Editorial team. In order to implement the mission indicated above I am going to continue the work of M.K.R. and Carmen. I also hope that they will share their experience with me, if I ask them for help, in particular if plans to enhance the Newsletter appear. This Issue of the Newsletter has been edited jointly by Carmen and myself with an invaluable support by Joyce.

I am looking forward to working with the EDS Officials, who provide messages to the Society through the Newsletter, with the EDS Technical Committees and with the EDS Staff, providing the Newsletter issues with a lot of technical information on the Society daily activities. I am looking forward to collaborating with the Regional Editors who publicize various activities, news, and highlights of Young Professionals, EDS chapters and members. I am also looking forward to communicating with organizers of the technical meetings and conferences, to publicize in advance and report these events for the benefit of EDS members and Newsletter readers. I also would like to maintain, and enhance, if possible, information on EDS Distinguished Lectures, DL Mini-Colloquia, webinars, i.e. platforms helpful for publicizing ED technology issues among the Newsletter readers.

As well, following the first message from Carmen as the EiC, I would like to invite the EDS members and readers to share with the Editorial Board their ideas on themes they would like to appear in the Newsletter and feedback on changes you see in the Newsletter in the coming years.

Finally, let me share a message with you, that a new member is joining the Editorial team. Dr. Kateryna Arkhypova from O.Ya. Usikov Institute for Radiophysics and Electronics of the National Academy of Sciences of Ukraine (IRE NASU) has been appointed as the Regional Editor for Region 8 Eastern Europe. It is my pleasure to welcome her in our team. Dear Kateryna, I wish you a fruitful work for the EDS community.

Kateryna Arkhypova

Kateryna Arkhypova (M'15-SM'19) received the M.S. and Ph.D. degrees in Biophysics from V.N. Karazin Kharkiv National University, Ukraine, in 2006 and 2012,

respectively. Since 2005 she has been with O.Ya. Usikov Institute for Radiophysics and Electronics, NAS of Ukraine, where she is now a Senior Researcher. Her research interests are oriented towards clinical applications of microwaves for diagnostic and therapeutic purposes. Dr. Arkhypova has more than 10 years of experience in multidisciplinary scientific cooperation with life scientists (primarily, medical doctors, biologists, and biochemists). She is an active IEEE volunteer. She is a Chairperson of the IEEE Ukraine Section (East) AP/MTT/ED/ AES/GRS/NPS Societies Joint Chapter as well as a TPC member of various international conferences such as European Microwave Conference. IEEE MTT-S International Microwave Bio-Conference, IEEE Ukrainian Microwave Week, etc. Since 2019, she also serves as the EuMA General Assembly member representing Group 10 (Armenia, Azerbaijan, Georgia, Moldova, and Ukraine).

Sincerely, Daniel Tomaszewski Editor-in Chief, EDS Newsletter e-mail: dtomasz@ite.waw.pl

#### Message from EDS VICE President for Regions AND CHAPTERS

Murty Polavarapu EDS Vice President of Regions and Chapter

It is my privilege to serve the members of EDS as Vice President for Regions and Chapters for 2020-2021. It is particularly gratifying for me since my first IEEE volunteer role was as the EDS Chap-

ter Chair in the Washington, DC area.

Chapters are geographical units of our Society and provide resources to members at local level for professional networking and learning. At Chapter meetings, you can develop and nurture professional relationships with your peers in the local area and get to meet leading authorities in your field who volunteer their time to share their knowledge of latest developments in an informal setting. As a volunteer at Chapter level, you can further develop your IEEE network and be able to assume roles with increasing responsibility in the world's largest professional society.

There are over 200 EDS Chapters worldwide and chances are that there is an EDS Chapter in your geographical area. You can find your local chapter at https://eds.ieee.org/chapters/ global-chapters-list. The EDS provides significant resources to Chapters in the form of funding for Distinguished Lecturers, Mini-colloquia and Chapter subsidies. In addition, the best performing Chapters are recognized annually with awards. More information on these resources is available on the EDS website https://eds.ieee.org/.

Each IEEE Chapter is connected to a local geographic Section. As such, a Chapter has two parents-Section and Society. Financial support for active Chapters (also known as annual rebate) is available through Sections from IEEE Member and Geographic Activities (MGA). Sections are also expected to provide support to Chapters in financial management and communications to all local members (beyond the EDS members). The vTools platform provided by MGA is a valuable resource to all local units in organizing meetings and in reaching the target audience electronically. For more information visit https://site. ieee.org/vtools/.

EDS also has many Student Branch Chapters based at educational institutions. With the normal expectation of student turnover, these units face severe challenges in organizing activities and maintaining membership. The faculty advisors can play an important role here in mentoring students and in instilling in them the value of belonging to a professional society.

Lack of new volunteers is frequently cited as the main reason for many chapters being inactive. Volunteer recruitment is not easy if you are trying to get someone to make a commitment to fill a role at the Chapter level for a full year. You may want to ease a potential volunteer into Chapter activities by asking for help with a small task, for example, for finding a venue for the next Chapter meeting. This is called 'microvolunteering' and if you can get ten people to help with small tasks, at least one of them most

probably will volunteer for the longer term. Give it a try!

From the governance perspective at the Society level, these geographic activities come under the purview of Regions/Chapters Committee and at a Regional level by the Subcommittees for Regions and Chapters (SRCs). I am deeply thankful for all the senior volunteers who have accepted the responsibilities on these Committees. The SRCs are expected to play an active role in nurturing Chapters in their geographical areas and provide resources as needed. SRCs are also called upon to help assess the viability of new chapters and mentor weak chapters. I hope to leverage the knowledge and networks of the members of the Regions/Chapters Committee and the SRCs in reenergizing our Chapters.

I urge you to seek out your local chapter and get involved as a volunteer or at least offer to share the results of your work at a meeting. You will find it a rewarding experience!

> Murty Polavarapu EDS Vice President of Regions and Chapter Space Electronics Solutions

More information available at https:// eds.ieee.org/about-eds/governance/ standing-committees/regions-chap ters-committee

Subcommittee Roster for Regions and Chapters available at https:// eds.ieee.org/about-eds/governance/ standing-committees/subcommitteefor-regions-chapters

### ANNOUNCEMENT OF NEWLY ELECTED OFFICERS & BOG MEMBERS

The Electron Devices Society (EDS) Officers and Board of Governors (BoG) members-at-large election was held on December 8, 2019 in San Francisco, CA. I am pleased to present the results of this election and short biographical information of the incoming team that will lead EDS in the years to come.

#### **OFFICERS**

The following volunteers were elected as Officers beginning 1/1/2020:

#### **President-Elect**

Ravi Todi received his doctoral degree in electrical engineering from the University of Central Florida (UCF), Orlando, Florida. In his ear-

ly career as an advisory engineer/scientist at the semiconductor research and development center at IBM microelectronics, his work was focused on high performance eDRAM integration on 45-nm silicon-on-insulator logic platform. For his many contributions to the success of eDRAM program at IBM, Ravi was awarded IBM's prestigious outstanding technical achievement award. In 2012, Ravi Joined Qualcomm for 20-nm product development and foundry management group, responsible for Qualcomm's foundry engagement with leading foundries. In 2015, he joined GLOBALFOUNDRIES, as the director of 14-nm product-line management, where he and his team were responsible for driving the technical and business results of the 14-nm FinFET product offerings. Currently he is with the Western Digital as a Sr. Technologist responsible for foundry technology development for global ASICs. With over 60 US granted patents, over 30 peer-reviewed journal publications, over 40 international conference presentations, and over 50 invited distinguished lectures, Ravi is well known in the semiconductor industry as a technical/business leader. He is a Fellow of the IEEE, a distinguish lecturer of IEEE EDS and serves as an editor of the IEEE Transactions on Electron Devices. He has served as an IEEE EDS Treasurer for four years, an elected BOG member, and as the Vice President of Technical Activities and conferences. Currently, he is the President-Elect of IEEE EDS.

#### **Treasurer**

Bin Zhao received his Ph.D. degree from California Institute of Technology. He has been with SEMATECH, Rockwell, Conexant, Skyworks,

Freescale, Fairchild, ON Semiconductor, and has worked on advanced VLSI technology development and design implementation of analog/mixed-signal, power management, and RF IC products. He has authored and coauthored over 200 journal publications and conference presentations, has authored three book chapters, and holds over 70 issued US patents. He has served as the Founding Co-Chair, Technical Working Group of RF and Analog/Mixed-Signal IC Technologies for Wireless Communications, International Technology Roadmap for Semiconductors (ITRS); IEEE EDS VP of Conferences; IEEE EDS VP of Publications; Chair, Editorial Steering Committee, IEEE Journal of Microelectromechanical Systems (J-MEMS); and Chair, IEEE Johnson Technology Award Committee. He is an IEEE Fellow and currently serving as the Chair of IEEE Conference Committee. He is a member of the IEEE Technical Activities Board, IEEE Publications Services and Products Board, and IEEE IoT Activities Board.

#### Secretary

MK Radhakrishnan is an academician and technical consultant in the field of electron device failure analysis and reliability, and founder director

of NanoRel LLP Technical consultants Singapore from 2004. Previously, he was a Senior Member of the Technical Staff at the Institute of Microelectronics, Singapore, an Adjunct Professor at the National University of Singapore, and a Scientist at the Indian Space Research Organization. Currently he is an Editor of the IEEE Journal of Electron Devices Society (JEDS). He has served as Editor of the Journal of Semiconductor Technology and Science and Guest Editor to IEEE TDMR. He was the Technical Chair of the IEEE IPFA in 1995 and 1997, General Chair of IPFA 1999 and IEEE IEDST 2009, and Co General Chair of IEEE EDTM 2019. As an IEEE EDS volunteer he served as an IEEE EDS Region 10 SRC Vice Chair, Regional Editor and the Editor in Chief of the EDS Newsletter, a member of the IEEE EDS Board of Governors, and IEEE EDS Vice President of the Regions & Chapters. He is an IEEE Life Senior member, Fellow of IETE, Member of the EDFAS and ESDA, and serves as an IEEE EDS Distinguished Lecturer.

#### **BoG Members-At-Large**

A total of seven members were elected for a three-year term (2019–2021). Two of the seven electees are serving a second term, while the other five have joined the board for the first time. The backgrounds of the electees span a wide range of professional and technical interests. The following are the results of the election and brief biographies of the individuals elected.

Constantin Bulucea received his MS (1962) and PhD (1974) degrees in EE

from the Polytechnic Institute of Bucharest. In 1969, he won a one-year scholarship for graduate studies at UC Berkeley.

Between 1970 and 1986, he led the R&D activities of Romania's Research Institute for Electronic Components, ICCE. In 1978, following the model of IEDM, he founded the Annual Conference for Semiconductors, now an international IEEE event. In the US, Dr. Bulucea worked for Siliconix, National Semiconductor, and TI (1987-2012) developing the first trench DMOS power transistors of the industry (Siliconix), and several high-performance analog CMOS processes (National Semiconductor). His inventions are protected in 69 US patents. Dr. Bulucea has been an editor of SSE (1978-2012), IEEE EDL (1995-2012), and IEEE J-EDS (2013 -). He is an Honorary Member of the Romanian Academy and an IEEE Life Fellow. In 2018 and 2019 he was on the IEEE/ EDS Fellow Evaluation Committee.

**Daniel Camacho** M.Sc. Received his BSEE from the Pontificia Universidad Javeriana in Bogota, Colombia in September 2007. He was awarded

the 2008 IEEE EDS Master Student Fellowship for his research work. In 2009 he received his Master's degree from Southern Methodist University in Dallas, Texas. He joined the Intel Corporation in 2010, where he has been since. His expertise is focused on high-performance analog and mixed-signal circuits, and clock generation and distribution.

John Dallesasse is a Professor of Electrical and Computer Engineering at the University of Illinois at Urbana-Champaign and has over 20 years of industry experience in technology development and executive management. Prior to joining UIUC he was

the Chief Technology Officer, Vice President, and cofounder of Skorpios Technologies developing innovative methods for heterogeneous

integration of compound semiconductors with silicon. His technical contributions include, with Nick Holonyak, Jr., the discovery of III V Oxidation, which has become an enabling process technology for the fabrication of Vertical-Cavity Surface-Emitting Lasers (VCSELs) for optical networking, 3D imaging, and LIDAR applications. John has a strong publication history and 45 issued patents. He serves as the Secretary of the Steering Committee for the IEEE Journal of Lightwave Technology and is the Chair of the Steering Committee for the IEEE Transactions on Semiconductor Manufacturing. He is a Fellow of the IEEE and OSA.

Mario Lanza received his PhD (with honors) in Electronic Engineering in 2010 at the Universitat Autonoma de Barcelona. In 2010-2011

he was NSFC postdoc at Peking University, and in 2012-2013 he was a Marie Curie fellow at Stanford University. Currently, he is a Full Professor in Nanoelectronics as Soochow University, where he leads a group formed by 17-20 graduate students and postdocs. His research focuses on the improvement of electronic devices using 2D materials. Prof. Lanza has published over 120 research papers (including Science, Nature Electronics, IEDM) edited a book for Wiley-VCH, and registered four patents, one of them granted with 1 million USD investments. He is member of the technical committee of several conferences (IEDM, IRPS, IPFA) and journals (Advanced Electronic Materials, Nature Scientific Reports, Nanotechnology). Prof. Lanza has received several world-class awards in his field of research, and he is a Distinguished Lecturer of the Electron Devices Society.

Geok Ing Ng received his Ph.D degree from the University of Michigan, Ann Arbor in 1990. Since joining the Nanyang Technologi-

cal University (NTU) Singapore in the School of EEE in 1996, he has held several key appointments including the Head of Microelectronics Division and Founding Directors of Microsystem Technologies Development Centre. He is currently the Director of the Center for Microsystems in TL@NTU and the Centre of Micro- and Nano-Electronics in EEE. He has published more than 300 international journal and conference papers and delivered plenary and invited talks at several international conferences in the areas of III-V low bandgap (InP) and large bandgap (GaN) compound semiconductors. He has been active in serving IEEE in various capacities including Steering Committee Member, 2020 IEEE Electron Device Technology and Manufacturing (EDTM) Conference, General Co-Chair, 2019 IEEE EDTM Conference, Guest Editor of Special Section of IEEE Transactions on Nanotechnology.

Claudio Paoloni received the degree cum laude in Electronic Engineering from the University Rome "Sapienza", Italy, in 1984. Since

2012, he has been Cockcroft Chair with the Engineering Department, Lancaster University, U.K. Since 2015, he has been the Head of Engineering Department. He is IEEE Senior member and Senior Fellow of the Higher Education Academy. He is Chair of the IEEE Electron Devices Society Vacuum ElectronicsTechnicalCommittee(2017–present). He was a Guest Editor for the Special Issue of the Transactions on Electron Devices on Vacuum Electronics (June 2014). He organized numerous international conferences and workshops, on vacuum electronics, millimetre wave and terahertz communications and technology. He is coordinator of two European Commission Horizon 2020 projects, TWEETHER and ULTRAWAVE. He is the author of more than 230 articles in international journals and conferences in the field of high frequency electronics, millimetre waves and THz vacuum electronics devices, and wireless communications.

Hitoshi Wakabayashi (M'00) received the M.E. and Ph.D. degrees in electrical engineering from the Tokyo Institute of Technology, Japan, in 1993 and

2003, respectively. He was with NEC Corporation from 1993 to 2006, the Massachusetts Institute of Technology from 2000 to 2001, and Sony Corporation from 2006 to 2012. He has been with the Tokyo Institute of Technology since 2013. He has served as the General Chairs

for the Symposium on VLSI Technology 2013, EDTM 2018, and IWJT 2017/2019.

I welcome all electees and urge them to get fully engaged in the affairs of the Electron Devices Society. EDS is a volunteer-led volunteerdriven organization and we expect the incoming volunteer leaders will continue this tradition going forward.

> Samar Saha 2019 EDS Nominations and Elections Chair Prospicient Devices Milpitas, CA

#### IN MEMORY OF HARVEY C. NATHANSON

BY JOACHIM N. BURGHARTZ

On Friday, November 22, 2019, at age 83, Harvey C. Nathanson peacefully passed away at home while with his loving family. Shortly prior to that date I happened to finish the article "Marvels in MEMS Evolvement and Development-Silicon as a Micromechanical Material has been Driving More-than-Moore" which recently appeared in the EDS Newsletter of January 2020 as part of the series "Marvels of Microelectronic Engineering, Harvey Nathanson played the most significant role in that article in which the key achievements and developments as well as the people behind MEMS were highlighted. Harvey Nathanson was the father of the MEMS. His work can be considered the first step into surface micromachining, in which the planar wafer processes were exploited for shallow three-dimensional micromechanical structures above of the bulk silicon wafer. What he started in the 1960's has become the foundation of MEMS devices which today can be found in virtually any commercial and consumer application. Reaching the high age of 83, Harvey Nathanson could enjoy seeing the blossom of his work.

Esther Mishelevich Nathanson, his wife, told me about his life and career,

which already was highlighted in an obituary in the Pittsburgh Gezette on November 23/24, 2019: He grew up in Pittsburgh as the son of a pharmacist and remained to stay there for all his life. As a boy in the 1950s, he taught himself about electrical circuits and built hi-fi music systems from mailorder kits. Instead of stepping into the footsteps of his father and take over the family pharmacy business he went to Carnegie Tech, now Carnegie Mellon University, where he earned his MS and Ph.D. degrees, both in electrical engineering. He joined Westinghouse Electric in Pittsburgh, working at Westinghouse Research Labs in Churchill. In 1965 he thought of a microscopic device used as a tuner for microelectronic radios. The invention, known as the resonant-gate transistor, became the first device in the field of micro-electro-mechanical systems (MEMS). This technology is now found in consumer products ranging from iPhones to automobiles. Harvey Nathanson also pioneered a method of mass production that would later become a mainstay of MEMS manufacturing. In 1973, he patented the use of tiny mirrors to create a video display of the type now found in digital projectors. In 1988 he became Chief Scientist of Westinghouse Research Labs, from where he retired in 2001 but continued to consult for another decade, completing a 50-year career in which he was awarded more than 50 patents in the field of solidstate electronics. In 2000 Nathanson was awarded the Millennium Medal by the Institute of Electrical and Electronics Engineers for "outstanding contributions to the Society and to the field of electron devices."

Harvey Nathanson is one of the great pioneers in the broader field of electron devices. We consider it an honor to further build on his ideas.

#### AWARDS AND CALL FOR NOMINATIONS

#### MEYYA MEYYAPPAN WINS TECHNOLOGY CHAMPION AWARD FOR FLEXIBLE ELECTRONICS

SEMI-FlexTech gives the FLEXI Awards each year to the winners for outstanding achievements in Flexible Hybrid Electronics (FHE).

Meyya Meyyappan, current EDS President, received the 2020 Technology Champion FLEXI Award for "his technical leadership in printed and flexible electronics, outreach activities and tireless volunteering to promote the field" at the FLEX 2020 Conference in San Jose, California. on February 26, 2020. FLEXIs have been the industry's premier award for distinguished organizations and individuals in the FHE sector since 2009. The awards are sponsored by SEMI-Flex Tech, an organization dedicated to the success of the FHE

#### 2020 IEEE EDS ROBERT BOSCH MICRO AND NANO ELECTRO MECHANICAL SYSTEMS AWARD WINNER

The 2020 IEEE EDS Robert Bosch Micro and Nano Electro Mechanical Systems Award was presented to Ming C. Wu, University of California, Berkeley, CA, USA, at the 2020 IEEE MEMS Conference, Vancouver, Canada, January, 2020. This prestigious award recognizes and honors advances in the invention, design, and/or fabrication of micro- or nano-electromechanical systems and/or devices.

Ming C. Wu is the Nortel Distinguished Professor of Electrical Engineering and Computer Sciences at University of California, Berkeley, and Co-Director of Berkeley Sensor and Actuator Center (BSAC). He received his PhD from UC Berkeley in 1988 and ioined its faculty in 2004 after working at AT&T Bell Laboratories and UCLA. He has published 600 papers and holds 30 US patents in Optical MEMS, optofluidics, silicon photonics and optoelectronics. In 1997, Prof. Wu co-founded OMM to commercialize MEMS optical switches. Recently, his

Ming C. Wu For pioneering contributions in MEMS optical switches and optoelectronic tweezers

group extended the switch array size to 240 x 240 by combining MEMS with silicon photonics. In 2011, Prof. Wu cofounded Berkeley Lights, Inc. to commercialize optoelectronic tweezers (OET) for single cell biology applications. Prof. Wu is an IEEE and Optical Society Fellow. His work has been recognized by the 2007 Paul F. Forman Engineering Excellence Award (OSA), the 2016 William Streifer Scientific Achievement Award (IEEE), and the 2017 C.E.K. Mees Medal (OSA).

> Kurt Petersen EDS Bosch Award Chair

### IEEE ROBERT BOSCH MICRO AND NANO ELECTRO MECHANICAL SYSTEMS AWARD

### Robert Bosch (1861-1942) Inventor, Entrepreneur, Founder of Robert Bosch GmbH

The Robert Bosch Micro and Nano Electro Mechanical Systems Award was established by the IEEE Electron Devices Society in 2014, to recognize and honor advances in the invention, design, and/or fabrication of micro- or nano-electromechanical systems and/or devices. The contributions to be honored by this award should be innovative and useful for practical applications.

This award is sponsored by the IEEE Electron Devices Society, with financial support from Robert Bosch LLC. It is intended that the award will be presented annually to an individual or to as many as three individuals whose achievements and contributions are judged to meet the selection criteria for the award. The award will be presented at an IEEE conference of the winner's choice. It is not necessary for the recipient(s) to be a member(s) of IEEE.

The recipient will receive a US\$10,000 honorarium, travel expenses to attend the award presentation, a bronze medal, and a certificate. In the event that more than one awardee is selected the cash honorarium will be equally divided among the recipients. Each recipient will receive a bronze medal and a certificate.

Please visit the EDS website for more information on this award: <a href="http://eds.ieee.org/robert-bosch-micro-and-nano-electro-mechanical-systems-award.html">http://eds.ieee.org/robert-bosch-micro-and-nano-electro-mechanical-systems-award.html</a>.

Nominations for this award should be made using our <u>online nomination form</u>, and submitted before midnight (EST) on October 2<sup>nd</sup>. Letters of recommendation must be sent directly to l.riello@ieee.org according to the same schedule.

#### 2019 IEEE EDS DISTINGUISHED SERVICE AWARD

The IEEE Electron Devices Society (EDS) is extremely proud of the services that it provides to its members. Its members generate the premier new developments in the field of electron devices and share these results with their peers and the world-at-large by publishing their papers in EDS journals and presenting results in its meetings. This is a global activity that is effective because of the efforts of numerous volunteers. Many of these volunteers labor in relative obscurity, with their only reward being the satisfaction that they receive in being an important part of a successful organization, namely of the IEEE Electron Devices Society. One means of thanking these volunteers is to recognize their contributions through the EDS Distinguished Service Award.

The recipient of the 2019 EDS Distinguished Service Award was Albert Wang, University of California, Riverside, CA, USA, and the award presentation took place at the International

Albert Wana, 2019 IEEE EDS Distinguished Service Award winner and Fernando Guarin, 2019 IEEE EDS President

Electron Devices Meeting (IEDM) in San Francisco, CA on December 9, 2019.